ARM-MP3-Player: Unterschied zwischen den Versionen

Keine Bearbeitungszusammenfassung |

(bastelt sonst überhaupt noch jemand?) |

||

| Zeile 1: | Zeile 1: | ||

von [[Benutzer:Andreas]] | von [[Benutzer:Andreas]] | ||

Ideensammlung zu einem ARM-basierten MP3-Player-Projekt, an dem | Ideensammlung zu einem ARM-basierten MP3-Player-Projekt, an dem ich gerade rumbastle: | ||

* CPU: AT91SAM7S256 (der einzige mit ausreichend RAM) | * CPU: AT91SAM7S256 (der einzige mit ausreichend RAM) | ||

Version vom 13. Mai 2006, 13:02 Uhr

von Benutzer:Andreas

Ideensammlung zu einem ARM-basierten MP3-Player-Projekt, an dem ich gerade rumbastle:

- CPU: AT91SAM7S256 (der einzige mit ausreichend RAM)

- MP3-Decoder: rein in Software, zur Wahl stehen Helix (erfolgreich getestet) und MAD (muss noch evaluiert werden)

- Datenspeicher: MMC/SD-Karte bzw miniSD oder RS-MMC, EFSL File System Library

Status

- AT91SAM7S64-Dev-Board, SAM7S64 gegen SAM7S256 ausgetauscht

- DAC: CS4331 (auf MP3-Player-Platine "Pump" aus der c't), Fütterung über SSC mit DMA

- Bild des Hardwareaufbaus

- Abspielen von WAV-Dateien von MMC/SD-Karte funktioniert

- Abspielen von MP3 aus dem internen Flash funktioniert (http://www.mikrocontroller.net/trac/browser/branches/at91-mmc/?rev=54)

- Problem: Abspielen von MP3 von der Karte. Lesen eines Frames von der Karte dauert 12ms, der Decoder braucht 18ms für einen Frame, ein Frame enthält Samples für 26ms -> keine Wiedergabe in Echtzeit möglich!

- Lösung (?): asynchroner Zugriff auf die Karte, Verwendung von DMA (-> während der Wartezeit und der Übertragung etwas anderes machen); FreeRTOS verwenden

DA-Wandler

Auswahl

MAX9850

- 28 PIN

- mit Kopfhörer-Amp. u.a.

- relativ aufwendige Beschaltung und Konfiguration

- auch krumme MCLK erlaubt:

- Anforderung im Integer mode: Takt ganzzahliges Vielfaches der 16fachen Samplerate => nur bei PLL-Multiplikator von 4 möglich

- Anforderung im Noninteger mode: Takt fast beliebig!

- => somit 44.1 kHz kein Problem, auch mit 18.432 MHz-Quarz

Wolfson WM8727

http://www.wolfson.co.uk/products/digital_audio/dacs/WM8727/

- 8-pin SOIC

- keine Konfiguration

- nicht sehr weit verbreitet

CS4331

http://joule.bu.edu/~hazen/DataSheets/Cirrus_Crystal/4330.pdf

- 8 pin SOIC

- keine Konfiguration

- nicht mehr hergestellt

CS4334

- 8-pin SOIC

- keine Konfiguration

- nur 5V-Betrieb

WM8731

- The WM8731 is a very low power, high quality audio codec with integrated headphone driver, designed for portable digital audio applications.

- Integrierte PLL-Takterzeugung aus z.B. 12 MHz

- Aufnahmefunktion möglich

- Mikro-Vorverstärker und Kopfhörer-Verstärker eingebaut

- Beschaffung?

TLV320AIC23B

- Kopfhörer-Verstärker

- 28 TSSOP

- läuft auch mit 12 MHz

- gibt's bei Digikey

TDA1543

- kein MCLK nötig

- DIP-8

- gibt's bei Segor für 2 Euro

- qualitätsmäßig eher Low-End

- -> perfekt zum Testen!

- Datenblatt: http://www.docethifi.com/TDA1543_.PDF

Taktversorgung

Prozessortakt: [math]\displaystyle{ f_c = 18\,432\,000 \mathrm{Hz} \cdot 3 = 55\,296\,000 \mathrm{Hz} }[/math]

Gewünschte Samplerate: [math]\displaystyle{ f_s = 44\,100 \mathrm{Hz} }[/math]

Bitrate am I2S: [math]\displaystyle{ f_b = f_s \cdot 2 \cdot 16 = 1\,411\,200 \mathrm{Hz} }[/math]

Erforderlicher Teiler: [math]\displaystyle{ \frac{f_c}{2 \cdot f_b} = 19.59 }[/math]

=> geht net, also Teiler=20 => Fehler

Bei 48 kHz Samplerate passt der 18.432 MHz-Quarz perfekt und kann direkt als MCLK für einen DAC genommen werden (Multiplikator 384 wird von praktisch allen unterstützt).

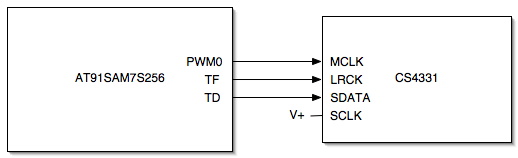

Ansteuerung des DAC (CS4331)

Hier wird der PWM-Controller für die MCLK-Erzeugung verwendet. SCLK wird vom Wandler intern erzeugt.

Das Problem ist hier, dass bei für USB geeigneter PLL-Frequenz (48 MHz) der Fehler der Samplerate relativ groß wird.

Dazugehörige Initialisierung (PLL für 48 MHz eingestellt):

/************ PWM ***********/ /* PWM0 = MAINCK/4 */ *AT91C_PMC_PCER = (1 << AT91C_ID_PWMC); // Enable Clock for PWM controller *AT91C_PWMC_CH0_CPRDR = 2; // channel period = 2 *AT91C_PWMC_CH0_CMR = 1; // prescaler = 2 pPIO->PIO_PDR = AT91C_PA0_PWM0; // enable pin *AT91C_PWMC_CH0_CUPDR = 1; *AT91C_PWMC_ENA = AT91C_PWMC_CHID0; // enable channel 0 output /************ SSC ***********/ *AT91C_PMC_PCER = (1 << AT91C_ID_SSC); // Enable Clock for SSC controller *AT91C_SSC_CR = AT91C_SSC_SWRST; // reset *AT91C_SSC_CMR = 16; *AT91C_SSC_TCMR = AT91C_SSC_CKS_DIV | AT91C_SSC_CKO_CONTINOUS | AT91C_SSC_START_FALL_RF | (1 << 16) | // STTDLY = 1 (15 << 24); // PERIOD = 15 pPIO->PIO_PDR = AT91C_PA16_TK | AT91C_PA15_TF | AT91C_PA17_TD; // enable pins *AT91C_SSC_TFMR = (15) | // 16 bit word length (1 << 8) | // DATNB = 1 => 2 words per frame (15 << 16) | // FSLEN = 15 AT91C_SSC_MSBF | AT91C_SSC_FSOS_NEGATIVE; *AT91C_SSC_CR = AT91C_SSC_TXEN; // enable TX