ARM-MP3-Player: Unterschied zwischen den Versionen

(Abspielen von MP3-Dateien von MMC/SD-Karte funktioniert) |

Keine Bearbeitungszusammenfassung |

||

| Zeile 1: | Zeile 1: | ||

von [[Benutzer:Andreas]] | von [[Benutzer:Andreas]] | ||

Jeder Mikrocontroller-Bastler der was auf sich hält baut irgend wann mal einen MP3-Player. Das hier ist meiner. | |||

* CPU: AT91SAM7S256 | * CPU: AT91SAM7S256 | ||

* [[MP3]]-Decoder: | * [[MP3]]-Decoder: https://datatype.helixcommunity.org/mp3dec.html | ||

* Datenspeicher: | * Datenspeicher: SD-Karte | ||

== Status == | == Status (13.06.06) == | ||

* AT91SAM7S64-Dev-Board, SAM7S64 gegen SAM7S256 ausgetauscht | * AT91SAM7S64-Dev-Board, SAM7S64 gegen SAM7S256 ausgetauscht | ||

| Zeile 16: | Zeile 16: | ||

== DA-Wandler == | == DA-Wandler == | ||

=== | === Ansteuerung des DAC (CS4331) === | ||

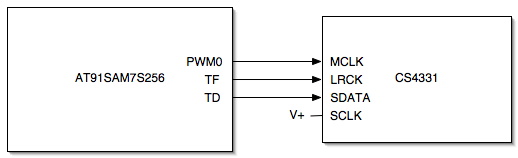

Für den ersten Prototypen verwende ich einen CS4331. Hier wird der PWM-Controller für die MCLK-Erzeugung verwendet, SCLK wird vom Wandler intern erzeugt. | |||

[[Bild:ARM-MP3-Blockschaltbild.png]] | |||

Der Prozessortakt ist hier auf 48.05 MHz eingestellt. Geteilt durch 4 gibt das einen etwas unpassenden Wert für den DAC (Soll: 256 * 44.1 kHz = 11.29 MHz, Ist: 12 MHz), somit hört sich alles etwas zu hoch an. | |||

Code zur Initialisierung: | |||

<pre class="code"> | |||

/************ PWM ***********/ | |||

/* PWM0 = MAINCK/4 */ | |||

*AT91C_PMC_PCER = (1 << AT91C_ID_PWMC); // Enable Clock for PWM controller | |||

*AT91C_PWMC_CH0_CPRDR = 2; // channel period = 2 | |||

*AT91C_PWMC_CH0_CMR = 1; // prescaler = 2 | |||

pPIO->PIO_PDR = AT91C_PA0_PWM0; // enable pin | |||

*AT91C_PWMC_CH0_CUPDR = 1; | |||

*AT91C_PWMC_ENA = AT91C_PWMC_CHID0; // enable channel 0 output | |||

/************ SSC ***********/ | |||

*AT91C_PMC_PCER = (1 << AT91C_ID_SSC); // Enable Clock for SSC controller | |||

*AT91C_SSC_CR = AT91C_SSC_SWRST; // reset | |||

*AT91C_SSC_CMR = 16; | |||

*AT91C_SSC_TCMR = AT91C_SSC_CKS_DIV | AT91C_SSC_CKO_CONTINOUS | | |||

AT91C_SSC_START_FALL_RF | | |||

(1 << 16) | // STTDLY = 1 | |||

(15 << 24); // PERIOD = 15 | |||

pPIO->PIO_PDR = AT91C_PA16_TK | AT91C_PA15_TF | AT91C_PA17_TD; // enable pins | |||

*AT91C_SSC_TFMR = (15) | // 16 bit word length | |||

(1 << 8) | // DATNB = 1 => 2 words per frame | |||

(15 << 16) | // FSLEN = 15 | |||

AT91C_SSC_MSBF | AT91C_SSC_FSOS_NEGATIVE; | |||

*AT91C_SSC_CR = AT91C_SSC_TXEN; // enable TX | |||

</pre> | |||

=== Taktversorgung === | |||

Soll-Werte: | |||

* Samplerate (word clock, LRCLK): <math>f_s = 44\,100 \mathrm{Hz}</math> | |||

* Bittakt: <math>f_b = f_s \cdot 2 \cdot 16 = 1\,411\,200 \mathrm{Hz}</math> | |||

Samplerate und Bittakt werden normalerweise synchron vom I2S-Interface erzeugt. | |||

* Master-Clock (MCLK): Fast alle DACs benötigen zusätzlich einen Takt mit dem 256-fachen der Samplerate, der exakt synchron zu den anderen Takten sein muss. In diesem Fall kann der DAC den Bittakt aus MCLK und LRCLK intern selbst erzeugen, so dass man den Bittakt nicht anzuschließen braucht. | |||

Um halbwegs zur üblichen Samplerate passende Takte zu erzeugen muss der Controller mit einer "krummen" Frequenz laufen (z.B. MCLK * 4 = 45.16 MHz). Das sollte sich mit der PLL hinbekommen lassen, allerdings wird es bei diesem Verhältnis zeitlich sehr knapp mit dem Dekodieren. | |||

Eine bessere Alternative sind DACs die intern einen sinnvollen Takt erzeugen und ausgeben können, so dass man das SSC peripheral des Controllers damit betreiben kann. Der Vorteil ist dass der Controller mit einer beliebigen Frequenz laufen kann. | |||

=== Interessante DACs === | |||

==== MAX9850 ==== | ==== MAX9850 ==== | ||

| Zeile 72: | Zeile 122: | ||

* -> perfekt zum Testen! | * -> perfekt zum Testen! | ||

* Datenblatt: http://www.docethifi.com/TDA1543_.PDF | * Datenblatt: http://www.docethifi.com/TDA1543_.PDF | ||

[[Category:Projekte]][[Category:ARM]] | [[Category:Projekte]][[Category:ARM]] | ||

Version vom 13. Mai 2006, 21:58 Uhr

von Benutzer:Andreas

Jeder Mikrocontroller-Bastler der was auf sich hält baut irgend wann mal einen MP3-Player. Das hier ist meiner.

- CPU: AT91SAM7S256

- MP3-Decoder: https://datatype.helixcommunity.org/mp3dec.html

- Datenspeicher: SD-Karte

Status (13.06.06)

- AT91SAM7S64-Dev-Board, SAM7S64 gegen SAM7S256 ausgetauscht

- DAC: CS4331 (auf MP3-Player-Platine "Pump" aus der c't), Fütterung über SSC mit DMA

- Bild des Hardwareaufbaus

- Abspielen von MP3-Dateien von MMC/SD-Karte funktioniert (ist aber seeehr knapp, muss optimiert werden!)

DA-Wandler

Ansteuerung des DAC (CS4331)

Für den ersten Prototypen verwende ich einen CS4331. Hier wird der PWM-Controller für die MCLK-Erzeugung verwendet, SCLK wird vom Wandler intern erzeugt.

Der Prozessortakt ist hier auf 48.05 MHz eingestellt. Geteilt durch 4 gibt das einen etwas unpassenden Wert für den DAC (Soll: 256 * 44.1 kHz = 11.29 MHz, Ist: 12 MHz), somit hört sich alles etwas zu hoch an.

Code zur Initialisierung:

/************ PWM ***********/ /* PWM0 = MAINCK/4 */ *AT91C_PMC_PCER = (1 << AT91C_ID_PWMC); // Enable Clock for PWM controller *AT91C_PWMC_CH0_CPRDR = 2; // channel period = 2 *AT91C_PWMC_CH0_CMR = 1; // prescaler = 2 pPIO->PIO_PDR = AT91C_PA0_PWM0; // enable pin *AT91C_PWMC_CH0_CUPDR = 1; *AT91C_PWMC_ENA = AT91C_PWMC_CHID0; // enable channel 0 output /************ SSC ***********/ *AT91C_PMC_PCER = (1 << AT91C_ID_SSC); // Enable Clock for SSC controller *AT91C_SSC_CR = AT91C_SSC_SWRST; // reset *AT91C_SSC_CMR = 16; *AT91C_SSC_TCMR = AT91C_SSC_CKS_DIV | AT91C_SSC_CKO_CONTINOUS | AT91C_SSC_START_FALL_RF | (1 << 16) | // STTDLY = 1 (15 << 24); // PERIOD = 15 pPIO->PIO_PDR = AT91C_PA16_TK | AT91C_PA15_TF | AT91C_PA17_TD; // enable pins *AT91C_SSC_TFMR = (15) | // 16 bit word length (1 << 8) | // DATNB = 1 => 2 words per frame (15 << 16) | // FSLEN = 15 AT91C_SSC_MSBF | AT91C_SSC_FSOS_NEGATIVE; *AT91C_SSC_CR = AT91C_SSC_TXEN; // enable TX

Taktversorgung

Soll-Werte:

- Samplerate (word clock, LRCLK): [math]\displaystyle{ f_s = 44\,100 \mathrm{Hz} }[/math]

- Bittakt: [math]\displaystyle{ f_b = f_s \cdot 2 \cdot 16 = 1\,411\,200 \mathrm{Hz} }[/math]

Samplerate und Bittakt werden normalerweise synchron vom I2S-Interface erzeugt.

- Master-Clock (MCLK): Fast alle DACs benötigen zusätzlich einen Takt mit dem 256-fachen der Samplerate, der exakt synchron zu den anderen Takten sein muss. In diesem Fall kann der DAC den Bittakt aus MCLK und LRCLK intern selbst erzeugen, so dass man den Bittakt nicht anzuschließen braucht.

Um halbwegs zur üblichen Samplerate passende Takte zu erzeugen muss der Controller mit einer "krummen" Frequenz laufen (z.B. MCLK * 4 = 45.16 MHz). Das sollte sich mit der PLL hinbekommen lassen, allerdings wird es bei diesem Verhältnis zeitlich sehr knapp mit dem Dekodieren.

Eine bessere Alternative sind DACs die intern einen sinnvollen Takt erzeugen und ausgeben können, so dass man das SSC peripheral des Controllers damit betreiben kann. Der Vorteil ist dass der Controller mit einer beliebigen Frequenz laufen kann.

Interessante DACs

MAX9850

- 28 PIN

- mit Kopfhörer-Amp. u.a.

- relativ aufwendige Beschaltung und Konfiguration

- auch krumme MCLK erlaubt:

- Anforderung im Integer mode: Takt ganzzahliges Vielfaches der 16fachen Samplerate => nur bei PLL-Multiplikator von 4 möglich

- Anforderung im Noninteger mode: Takt fast beliebig!

- => somit 44.1 kHz kein Problem, auch mit 18.432 MHz-Quarz

Wolfson WM8727

http://www.wolfson.co.uk/products/digital_audio/dacs/WM8727/

- 8-pin SOIC

- keine Konfiguration

- nicht sehr weit verbreitet

CS4331

http://joule.bu.edu/~hazen/DataSheets/Cirrus_Crystal/4330.pdf

- 8 pin SOIC

- keine Konfiguration

- nicht mehr hergestellt

CS4334

- 8-pin SOIC

- keine Konfiguration

- nur 5V-Betrieb

WM8731

- The WM8731 is a very low power, high quality audio codec with integrated headphone driver, designed for portable digital audio applications.

- Integrierte PLL-Takterzeugung aus z.B. 12 MHz

- Aufnahmefunktion möglich

- Mikro-Vorverstärker und Kopfhörer-Verstärker eingebaut

- Beschaffung?

TLV320AIC23B

- Kopfhörer-Verstärker

- 28 TSSOP

- läuft auch mit 12 MHz

- gibt's bei Digikey

TDA1543

- kein MCLK nötig

- DIP-8

- gibt's bei Segor für 2 Euro

- qualitätsmäßig eher Low-End

- -> perfekt zum Testen!

- Datenblatt: http://www.docethifi.com/TDA1543_.PDF