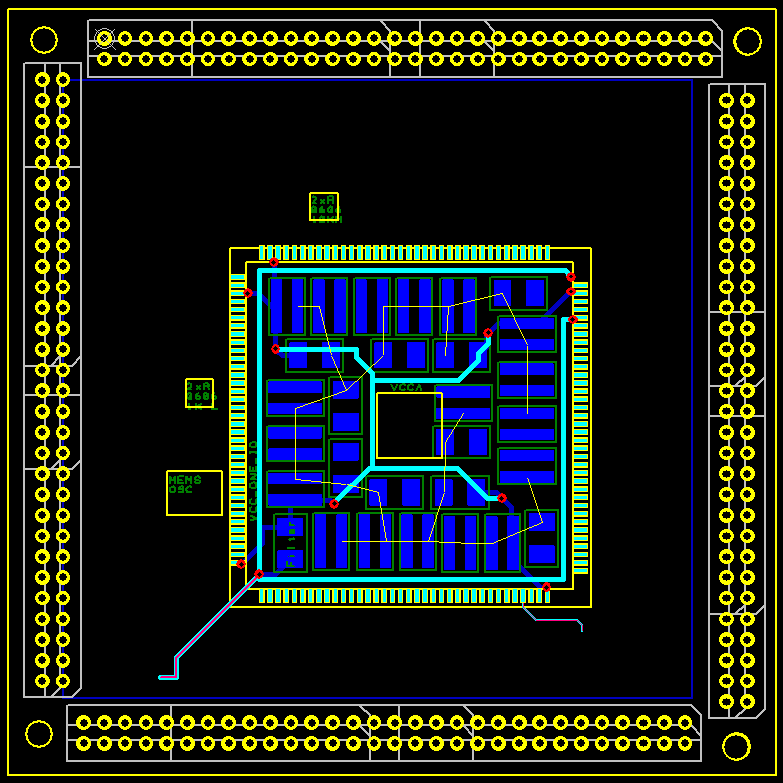

Altera Max10 Breakout Board

Warum Max10?

- Aktuell (Aug 2016) der einzig verfügbare FPGA in QFP bis 50K LUT.

- Eignung für geringe Stückzahlen, Handbestückung, Test/Inbetriebnahme

- Geringe BOM: Flash on package, single-supply

- 3 temperature grades für QFP: C,I,A

Eigenschaften des Breakout (11.08.16)

- 47mm x 47mm

- passt in Gehäuse mit Außenabmessungen 50mm x 50mm

- MEMS CLK mit CLK_enable

- 120 (4x30) pins single row 1.27

- davon I/O: 97

- auf Steckbrett nutzbar (jeder 2. Pin)

- optionale Bestückung double row für zusätzliche GND pins

Überschlagsrechnung BOM-Kosten 10M04SC

- 10M04SC, digikey 8,22 EUR (Abnahme 25 Stück) ODER

- 10M04SC, digikey 10,29 EUR (Abnahme 01 Stück)

- PCB, dirtypcb 0,65 USD (10mal 10x10 für 25USD -> 25/(10*4))

- MEMS CLK, digikey 1,00 EUR

- Caps (keine volle Bestückung für 04SC) 1,xx EUR

- Pin header, ebay/ali 0,35 EUR

10 bis 15 EUR

Anforderungen

- A1. OpenSource; Design einfach modifizierbar und verwendbar

- A2. Max10 04K LUT bis 50K LUT QFP single-supply

- A3. geringe Material-Kosten für kleine Stückzahlen

- A4. händisch lötbar, wenig Bauteile

- A5. Gute GND-Anbindung auf Ansteckmodule/Baseboards

- A6. Auf Steckbrett verwendbar

- A7. Mit 2.54mm Pinheadern verwendbar

- A8. Breakout von möglichst vielen I/Os

- SI. Signal Integrity; PDN. power distribution network

Spezifikation

- S1. Kicad-Design (A1)

- S2. Zwei PCBs mit Pin-kombatiblen Breakout für die package-Linien 04-25 und 40-50 (A2).

- Die pinouts dieser beiden package-Linien sind ähnlich aber nicht gleich.

- S3. 2-Layer-PCB; max 50mm x 50mm (A3, SI)

- S4. Mindestens 0603; Footprints für händische Bestückung (A4)

- S5. Single row 1.27mm THT pin header (A8, A3, A4)

- Anordnung/Distanz zueinander: Vielfaches von 2.54mm

- A6 erfüllt bei Nutzung jedes 2. pins (GND geeignet positionieren)

- A7 wie folgt erfüllt: Breakout auf 2.54mm double row mittels

- Adapter oder

- Ribbon cable mit Klemmstecker (Seite1: 1.27mm single; Seite2: 2.54 double)

- S6. Optionale Bestückung mit 1.27mm THT double row für zusätzliche GND pins (A5, SI)

Details (Spezifikation)

- D1. Pin header an allen 4 Seiten

- D2. Zwischen QFP und pin header: top layer für Signal; bottom layer GND (A5, SI)

- D3. (Fast) alle caps direkt unter das QFP (D2)

- D4. Möglichst wenig Überschneidungen der Power Traces (SI)

- D5. 0612 caps für HF decoubling (A4, SI, PDN)

- D6. Pcb thickness: 0.6mm oder 0.8mm (SI, PDN)

- D7. Leiterbahnbreite, spacings: 0.150mm; drill: 0.300mm (A3)

Bewertung ADC

- Den FPGA gibt es im QFP als SA (1Msps ADC) und als SC (ohne ADC). Beim FPGA beträgt der Preisunterschied zwischen SA und SC 4-8EUR. Ein 1Msps ADC kostet ca. 4EUR.

- Der ADC verursacht auch im deaktivierten Zustand einen Stromverbrauch an den ADC-Pins (Device Datasheet Seite 8)

- Bei Verwendung des ADC sind zusätzlich erforderlich: GND-ADC, VREF-ADC, VCC-ADC

- Dies ist zusätzlich auf 2 Lagen schwierig zu realisieren.

-> Zunächst auf ADC verzichten und erst einmal schauen, wie gut das PDN ohne die zusätzliche ADC-Beschaltung ist.

Betrachtung zum PDN

- In der Mitte des Package befindet sich ein GND-Pad. Dieses muss elektrisch gut von allen 4 Seiten mit der GND-Fläche verbunden werden.

- Anzahl supplies, filter

- Der Fall Single-Supply ohne ADC ist dargestellt in "Device Family Pin Connection Guidelines" auf Seite 32 und 33. Hier werden 2 regulators vorgeschlagen.

- Aus Datei "Device Family Pin Connection Guidelines":

- Auf Seite 33 wird ein Filter zwischen VCC_ONE und VCCA vorgeschlagen.

- Auf Seite 32 steht: "Both VCCA and VCC_ONE must share a single power source using proper isolation filter."

- Aus Datei "Power Management User Guide":

- Bildchen auf Seite 4: Die VCC_ONE pins und VCCA pins sind im Package direkt miteinander verbunden.

- Anfrage beim Support ergibt: VCCA pins und VCC_ONE pins sind im package NICHT miteinander verbunden.

- -> Spannungsversorgung des Boards über einen einzelnen 3V3-Pin.

- -> VCC_ONE und VCCO werden auf dem PCB gemeinsam als VCC_ONE_ geführt.

- -> VCCA wird über einen Filter realisiert

BOM für das breakout pcb 10M50:

- FPGA (1x 52EUR; 25x 44EUR)

http://www.digikey.de/product-detail/de/altera/10M50SCE144C8G/544-3129-ND/5284853

- 01x 0603 Filter

TODO lrs

- 10x 0603 47uF

- 18x 0612 1uF

- MEMS CLK an CLK0 oder CLK1

http://www.digikey.de/product-detail/de/silicon-labs/501JCA100M000CAG/336-2997-ND/4582107

- 1x 1K(2x) 0606 (config pull down)

http://www.digikey.de/product-detail/de/cts-resistor-products/742C043102JP/742C043102JPCT-ND/1124588

- 1x 10K(2x) 0606 (config pull up)

http://www.digikey.de/product-detail/de/cts-resistor-products/742C043103JP/742C043103JPCT-ND/1124587

- Pin header single row

http://www.ebay.de/itm/10Stk-50Pin-50P-1-27MM-Gold-Plated-Single-Row-Straight-Male-Pin-Header-Neu-/111543240426 http://www.ebay.de/itm/10Stk-50Pin-50P-1-27MM-Gold-Plated-Single-Row-Straight-Female-Pin-Header-Neu-/111543242032 ODER

- Pin header double row

http://www.aliexpress.com/item/10-pcs-1-27-mm-lapangan-2x50pin-ganda-baris-laki-laki-Pin-Header-Pin-konektor-Double/32384322952.html http://www.aliexpress.com/item/100pcs-lot-Du-Pont-1-27mm-Female-Header-2-36P-Straight-Double-Row-180o-Rohs-high/32352158974.html http://www.aliexpress.com/item/10Pcs-Pitch-1-27mm-2x50Pin-100-Pin-Female-Double-Row-Straight-Header-Connector-Socket/32707828068.html

- PCB

dirty pcb oder andere

Arbeitspakete

P1 Config pins (DONE)

Aufgeführt werden alle config-Pins, die beschalten werden (müssen):

- CONFIG_SEL -> GND

- CONF_DONE -> 10K pull-up (QFP top, dunkel-gelb)

- nCONFIG -> VCC_ONE_IO

- nSTATUS -> 10K pull-up (QFP top, dunkel-gelb)

- TCK -> 1K pull-down (QFP left, hell-gelb)

- JTAGEN -> 1K pull-down (QFP left, hell-gelb)

- Die JTAG pins werden als JTAG oder als I/O genutzt.

- (Abhängig von der Beschaltung JTAGEN sowie von Bitstream-Optionen)

- Andere config pins dürfen floating sein.

P2 Betrachtung Clocks (done):

- Im Datenblatt wird auf eine relativ hohe Kopplung der pins im

E144-package hingewiesen. Datenleitungen sollten nicht direkt neben einem CLK pin mit "hoher" Frequenz angeschlossen werden.

- CLK auf dem PCB:

- MEMS_CLK und CLK_EN:

- CLK0p/n oder CLK1p/n (QFP left)

- Beide CLK0 und CLK1 sind in allen densities (4K -50K) auf der linken Seite vorhanden.

- 10M04 besitzt weniger PLLs und weniger CLK-Eingänge. Nach Möglichkeit sollten auch beim PCB mit 10M04 mindestens ein CLK-Eingang auf der linken Seite und ein CLK-Eingang auf der rechten Seite verfügbar sein. Dies sollten dann beim 10M50 ebenfalls CLK-Eingänge sein, um pin-Kompatibilität der breakout-pcbs zu gewährleisten.

P3 Betrachtung Unterschiede 10M04 pinout vs 10M50 pinout (done):

- 10M04:

- 10M50:

- VCC, VCCO und GND liegen teilweise unterschiedlich -> für das breakout unkritisch.

- Am package des M04SC befindet sich auf der linken Seite zwischen den JTAG pins (orange) ein I/O pin (grün). Wird dieser pin nicht zum pin-header des pcb herausgeführt, so ist die Pinbelegung des pcb für beide package-Linien (04-25 und 40-50) auch hinsichtlich JTAG sowie hinsichtlich CLK0,1 identisch.

- CLK0,1,2,3 identisch

- PLL_L_CLKOUT identisch

P4 Anordnung der caps und Führung der Power traces (DONE)

P5 Schematic Symbole und PCB footprints erstellen (TODO)

- ggf. mit https://github.com/xesscorp/KiPart

P6 Layout für breakout pcbs erstellen (TODO lrs)

- erfordert P5

P7 Bestückung (TODO)

- erfordert P6

P8 Basebord1 Schematic TODO)

- (̶f̶̶ü̶̶r̶̶ ̶̶p̶̶e̶̶r̶̶f̶̶o̶̶r̶̶m̶̶a̶̶n̶̶c̶̶e̶-̶t̶̶e̶̶s̶̶t̶̶s̶)

- ̶̶i̶/̶o̶-̶p̶̶i̶̶n̶̶s̶̶ ̶̶d̶̶e̶̶s̶̶ ̶̶f̶̶p̶̶g̶̶a̶̶ ̶̶m̶̶i̶̶t̶̶e̶̶i̶̶n̶̶a̶̶n̶̶d̶̶e̶̶r̶̶ ̶̶v̶̶e̶̶r̶̶b̶̶i̶̶n̶̶d̶̶e̶̶n̶

- Dafür kann man auch 2 breakout boards aufeinander stecken und gegeneinander testen.

- JTAG

- Jumper für configpin JTAGEN

- USB conn

- LDO an USB conn

P9 Basebord1 Layout (TODO)

- erfordert P7, P8

P10 Inbetriebnahme mit Baseboard (TODO)

- erfordert P7, P9

P11 Basebord2 Schematic (optional, TODO)

- JTAG

- Jumper für configpin JTAGEN

- USB conn

- LDO an USB conn

- Pinheader für typisches NRF24

- Footprint für ESP8266

- Pin header für FTDI UM232H-B (oder ähnlich)

- Pin header für wiz850io

- ...?

P12 Basebord2 Layout (optional, TODO)

- erfordert P7, P11

Weitere Ideen:

- ̶S̶̶D̶̶R̶̶A̶̶M̶̶ ̶̶m̶̶i̶̶t̶̶ ̶̶r̶̶e̶̶d̶̶u̶̶z̶̶i̶̶e̶̶r̶̶t̶̶e̶̶m̶̶ ̶̶p̶̶i̶̶n̶̶ ̶̶c̶̶o̶̶u̶̶n̶̶t

- Besser: HyperRAM

- 2x ADV7513 HDMI

...